### Application Note AN-1085<sub>revC</sub>

### IRS2153(1)D and IR2153(1)/IR2153(1)D Comparison

#### Table of Contents

| Introduction                                                                | Page |

|-----------------------------------------------------------------------------|------|

| Block Diagrams                                                              | . 2  |

| IR2153(1)/IR2153(1)D vs. IRS2153(1)D Electrical Characteristics Differences | . 4  |

| Conclusions                                                                 | 7    |

#### 1. INTRODUCTION

The new IRS2153(1)D replaces the existing IR2153(1)/IR2153(1)D HVICs advantageously by saving the need for an external bootstrap diode. It is based on the same core design and is pin-to-pin compatible, allowing minimum changes to the previous design. This application note describes the differences between the existing IR2153(1)/IR2153(1)D IC family and the new IRS2153(1)D.

#### 2. BLOCK DIAGRAMS

The IR2153(1)/IR2153(1)D is not a single IC, but consists of a family of ICs (Table I).

| P/N          | Deadtime (typ.) | Internal Bootstrap Diode | Package Type |

|--------------|-----------------|--------------------------|--------------|

| IR2153PbF    | 1.2 µs          | No                       | DIP8         |

| IR2153SPbF   | 1.2 µs          | No                       | SO8          |

| IR21531PbF   | 0.6 µs          | No                       | DIP8         |

| IR21531SPbF  | 0.6 µs          | No                       | SO8          |

| IR2153DPbF   | 1.2 µs          | Yes                      | DIP8         |

| IR2153DSPbF  | 1.2 µs          | Yes                      | SO8          |

| IR21531DPbF  | 0.6 µs          | Yes                      | DIP8         |

| IR21531DSPbF | 0.6 µs          | Yes                      | SO8          |

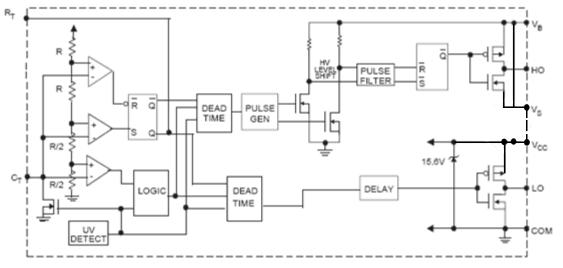

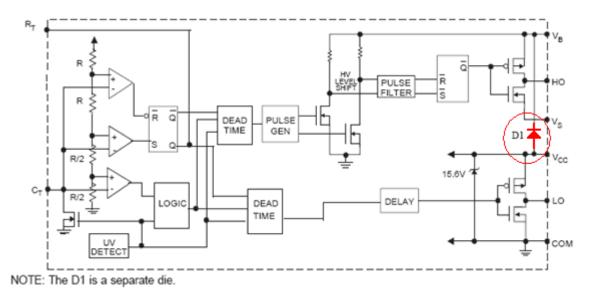

The functional block diagrams of each IC (Figs. 1 and 2) are exactly the same except the internal bootstrap diode.

Figure 1: IR2153(1) Functional Block Diagram

Figure 2: IR2153(1)D Functional Block Diagram

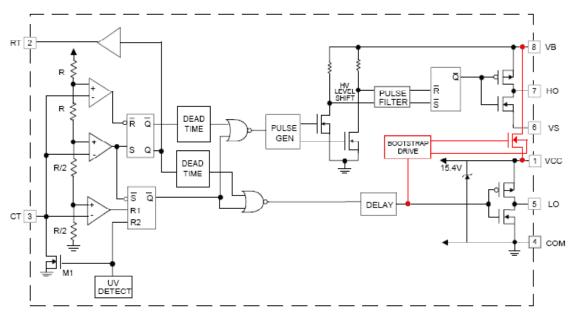

In the new IRS2153(1)D IC (Fig. 3), an internal FET now replaces the internal bootstrap diode, which was previously a separate die. IRS2153(1)D has the same functionality as IR2153(1)D and the need for an additional diode has been eliminated.

Figure 3: IRS2153(1)D Functional Block Diagram

<u>Consequently:</u> a customer using IR2153(1)/IR2153(1)D should take particular care of the bootstrap circuitry when switching to IRS2153(1)D.

#### 3. IR2153(1)/IR2153(1)D vs. IRS2153(1)D ELECTRICAL CHARACTERISTICS DIFFERENCES

The following tables and comments highlight the differences between the IR2153(1)/IR2153(1)D and the new IRS2153(1)D:

|                     | Parameter                                                                                | IR2153(1) | /IR2153(1)D | IRS2     | 153(1)D   | Unito |

|---------------------|------------------------------------------------------------------------------------------|-----------|-------------|----------|-----------|-------|

| Symbol              | Definition                                                                               | min       | max         | min      | max       | Units |

| VB                  | High side floating supply voltage                                                        | -0.3      | 625         | -0.3     | 625       |       |

| Vs                  | High side floating supply offset voltage                                                 | VB - 25   | VB + 0.3    | VB - 25  | VB + 0.3  | v     |

| V <sub>HO</sub>     | High side floating output voltage                                                        | VS - 0.3  | VB + 0.3    | VS - 0.3 | VB + 0.3  |       |

| V <sub>LO</sub>     | Low side output voltage                                                                  | -0.3      | VCC + 0.3   | -0.3     | VCC + 0.3 |       |

| I <sub>RT</sub>     | RT pin current                                                                           | -5        | 5           | -5       | 5         | mA    |

| V <sub>RT</sub>     | RT pin voltage                                                                           | -0.3      | VCC + 0.3   | -0.3     | VCC + 0.3 | V     |

| V <sub>CT</sub>     | CT pin voltage                                                                           | -0.3      | VCC + 0.3   | -0.3     | VCC + 0.3 | v     |

| lcc                 | Supply current (Note 1)                                                                  |           | 25          |          | 20        | mA    |

| IO <sub>MAX</sub>   | Maximum allowable current at LO and HO due to<br>external power transistor Miller effect |           |             | -500     | 500       | ША    |

| dV <sub>S</sub> /dt | Allowable offset voltage slew rate                                                       | -50       | 50          | -50      | 50        | V/ns  |

| PD                  | Max. power dissipation @ TA $\leq$ +25 °C, 8-Pin DIP                                     |           | 1.0         |          | 1.0       | W     |

| PD                  | Max. power dissipation @ TA $\leq$ +25 °C, 8-Pin SOIC                                    |           | 0.625       |          | 0.625     |       |

| Rthja               | Thermal resistance, junction to ambient, 8-Pin DIP                                       |           | 125         |          | 85        | °C/W  |

| Rthja               | Thermal resistance, junction to ambient, 8-Pin SOIC                                      |           | 200         |          | 128       |       |

| TJ                  | Junction temperature                                                                     | -55       | 150         | -55      | 150       |       |

| Ts                  | Storage temperature                                                                      | -55       | 150         | -55      | 150       | °C    |

| TL                  | Lead temperature (soldering, 10 seconds)                                                 |           | 300         |          | 300       |       |

#### Absolute Maximum Ratings

**Comments:** All absolute maximum ratings are exactly the same except for the maximum supply current limit and the thermal resistance. The maximum supply current is rated at 20 mA for the new IRS2153(1)D versus 25 mA for the IR2153(1)/IR2153(1)D and is due to the internal zener clamp. A 20 mA maximum versus 25 mA should be a negligible amount for most applications. A lower thermal resistance will give lower temperatures on the package surface.

#### **Recommended Operating Conditions**

|                 | Parameter                                             | IR2153(1)/I           | R2153(1)D | IRS2153(      | Units  |       |

|-----------------|-------------------------------------------------------|-----------------------|-----------|---------------|--------|-------|

| Symbol          | Definition                                            | min                   | max       | min           | max    | Units |

| $V_{\text{BS}}$ | High side floating supply voltage                     | V <sub>CC</sub> - 0.7 | VCLAMP    | VCC - 0.7     | VCLAMP |       |

| Vs              | Steady state high side floating supply offset voltage | -3.0                  | 600       | -3.0          | 600    | V     |

| Vcc             | Supply voltage                                        | 10                    | VCLAMP    | VCCUV+ + 0.1V | VCLAMP |       |

| Icc             | Supply current                                        |                       | 5         |               | 5      | mA    |

| TJ              | Junction temperature                                  | -40                   | 125       | -40           | 125    | °C    |

**Comments:** All parameters are mostly the same.

#### AN-1085

#### **Recommended Component Values**

|                | Parameter                   |     | R2153(1)D | IRS2153( | Units |       |

|----------------|-----------------------------|-----|-----------|----------|-------|-------|

| Symbol         | Definition                  | min | max       | min      | max   | Units |

| R <sub>T</sub> | Timing resistor value       | 1   |           | 1        |       | kΩ    |

| CT             | $C_{T}$ pin capacitor value | 330 |           | 330      |       | pF    |

**Comments:** All parameters are exactly the same.

#### **Electrical Characteristics**

| Bootstrap      | FET/Diode Characteristics                    | IR2153(1)/IR2153(1)D |     |     | IR  | S2153(1 | )D  | Units | Test                    |  |

|----------------|----------------------------------------------|----------------------|-----|-----|-----|---------|-----|-------|-------------------------|--|

| Symbol         | Definition                                   | Min                  | Тур | Max | Min | Тур     | Max | Units | Conditions              |  |

| V <sub>F</sub> | Bootstrap diode forward voltage (IR2153(1)D) | 0.5                  |     | 1.0 |     |         |     | V     | I <sub>F</sub> = 250 mA |  |

| VB_ON          | VB when the bootstrap FET is on              |                      |     |     |     | 13.7    |     | •     |                         |  |

| IB_CAP         | VB source current when bootstrap FET is on   |                      |     |     | 40  | 55      |     | mA    | CBS=0.1 µF              |  |

| IB_10V         | VB source current when bootstrap FET is on   |                      |     |     | 10  | 12      |     |       | VB=10 V                 |  |

**Comments:** The IRS2153(1)D contains an integrated bootstrap MOSFET that eliminates the need for an external high-voltage bootstrap diode. The integrated bootstrap MOSFET is turned on only during the time when LO is 'high', and has a limited source current due to  $R_{DSon}$ . The V<sub>BS</sub> voltage will determined each cycle by on the on-time of LO, the size of the external MOSFETs and the value of the CBS capacitor. At start-up, several cycles of LO will occur first until V<sub>BS</sub> increases above V<sub>BSUV+</sub> (see Floating Supply Characteristics) and then HO will start to oscillate. The maximum operating frequency will be determined by the MOSFET driven by IRS2153(1)D and the value of the CBS capacitor since the bootstrap MOSFET needs to maintain V<sub>BS</sub> above V<sub>BSUV-</sub> each cycle. If the frequency is too high, V<sub>BS</sub> will fall below V<sub>BSUV-</sub> and the HO output will turn off. To avoid this problem, an external high-voltage bootstrap diode can be added in parallel to maintain V<sub>BS</sub> above V<sub>BSUV-</sub> during high-frequency applications.

| Low Voltage          | Low Voltage Supply Characteristics                     |      | (1)/IR21 | 53(1)D | IF   | RS2153( | 1)D  | Units | Test                    |

|----------------------|--------------------------------------------------------|------|----------|--------|------|---------|------|-------|-------------------------|

| Symbol               | Definition                                             | Min  | Тур      | Max    | Min  | Тур     | Max  | Units | Conditions              |

| V <sub>CCUV+</sub>   | Rising $V_{cc}$ undervoltage lockout threshold         | 8.1  | 9.0      | 8.1    | 10.0 | 11.0    | 12.0 |       |                         |

| V <sub>CCUV</sub> -  | Falling $V_{\text{CC}}$ undervoltage lockout threshold | 7.2  | 8.0      | 7.2    | 8.0  | 9.0     | 10.0 | V     |                         |

| V <sub>CCUVHYS</sub> | $V_{\text{CC}}$ undervoltage lockout hysteresis        | 0.5  | 1.0      | 0.5    | 1.6  | 2.0     | 2.4  |       |                         |

| I <sub>QCCUV</sub>   | Micropower startup $V_{cc}$ supply current             |      | 75       | 150    |      | 130     | 170  |       | $V_{CC} \leq V_{CCUV}$  |

| lacc                 | Quiescent V <sub>CC</sub> supply current               |      | 500      | 950    |      | 800     | 1000 | μA    |                         |

| Icc                  | V <sub>cc</sub> supply current                         |      |          |        |      | 1.8     |      | mA    | R <sub>T</sub> =36.9 kΩ |

| V <sub>CLAMP</sub>   | V <sub>cc</sub> zener clamp voltage                    | 14.4 | 15.6     | 16.8   | 14.4 | 15.4    | 16.8 | V     | I <sub>cc</sub> = 5 mA  |

**Comments:** No major changes other than  $V_{CCUV+}$  and  $V_{CCUV-}$  being higher, as well as the hysteresis. The higher UVLO thresholds should not impact the application since typically  $V_{CC}$  is regulated against its internal 15.4 V clamp voltage. The increased hysteresis should make the application more robust and prevent the IC from turning off momentarily should transient dips in the  $V_{CC}$  voltage occur.

| Floating S          | upply Characteristics                                                              | naracteristics IR2153(1)/IR2153(1)D IRS2153(1)D |     |     |     | )D  | Units | Test  |                                           |

|---------------------|------------------------------------------------------------------------------------|-------------------------------------------------|-----|-----|-----|-----|-------|-------|-------------------------------------------|

| Symbol              | Definition                                                                         | Min                                             | Тур | Max | Min | Тур | Max   | Units | Conditions                                |

| I <sub>QBS</sub>    | Quiescent $V_{BS}$ supply current                                                  |                                                 | 30  | 50  |     | 60  | 80    | μA    |                                           |

| V <sub>BSUV+</sub>  | $V_{\mbox{\scriptsize BS}}$ supply undervoltage positive going threshold           |                                                 |     |     | 8.0 | 9.0 | 9.5   | V     |                                           |

| V <sub>BSUV-</sub>  | $V_{\mbox{\scriptsize BS}}$ supply undervoltage negative going threshold           |                                                 |     |     | 7.0 | 8.0 | 9.0   | v     |                                           |

| I <sub>QBSUV-</sub> | Micropower startup $V_{BS}$ supply current                                         |                                                 | 0   | 10  |     |     |       | μA    | $V_{CC} \le V_{CCUV-,}$ $V_{CC} = V_{BS}$ |

| V <sub>BSMIN</sub>  | Minimum required $V_{BS}$ voltage for proper functionality from $R_{T}$ to $H_{O}$ |                                                 | 4.0 | 5.0 |     |     |       | V     | $V_{CC} = V_{CCUV} + 0.1 V$               |

| Ilk                 | Offset supply leakage current                                                      |                                                 |     | 50  |     |     | 50    | μA    | V <sub>B</sub> = V <sub>S</sub> = 600 V   |

**Comments:** The new IRS2153(1)D contains an under-voltage lockout circuit. This is necessary because of the additional integrated bootstrap MOSFET. The UVLO circuit will guarantee that  $V_{BS}$  is high enough before turning on  $H_O$  and will protect the external MOSFET from being driven in the linear region should  $V_{BS}$  decrease too much.

| Oscillator        | /O Characteristics                                                       | IR215 | 3(1)/IR21 | 53(1)D | IR   | S2153(1 | )D   | Units | Test Conditions                                     |

|-------------------|--------------------------------------------------------------------------|-------|-----------|--------|------|---------|------|-------|-----------------------------------------------------|

| Symbol            | Definition                                                               | Min   | Тур       | Мах    | Min  | Тур     | Мах  | Units | Test Conditions                                     |

| f                 | Oppillator fraguency                                                     | 19.4  | 20        | 20.6   | 18.4 | 19.0    | 19.6 | kHz   | R <sub>T</sub> = 36.9/36.5 kΩ                       |

| f osc             | Oscillator frequency                                                     | 94    | 100       | 106    | 88   | 93      | 100  | KI    | R <sub>T</sub> = 7.43/7.15 kΩ                       |

| d                 | $R_T$ pin duty cycle                                                     | 48    | 50        | 52     |      | 50      |      | %     | f <sub>o</sub> < 100 kHz                            |

| Ict               | C⊤ pin current                                                           |       | 0.001     | 1.0    |      | 0.02    | 1.0  | μA    |                                                     |

| I <sub>CTUV</sub> | UV-mode $C_T$ pin pulldown current                                       | 0.30  | 0.70      | 1.2    | 0.2  | 0.3     | 0.6  | mA    | $V_{CC}$ = 7 V                                      |

| V <sub>CT+</sub>  | Upper $C_T$ ramp voltage threshold                                       |       | 8.0       |        |      | 9.32    |      |       |                                                     |

| V <sub>CT-</sub>  | Lower $C_T$ ramp voltage threshold                                       |       | 4.0       |        |      | 4.66    |      | V     |                                                     |

| V <sub>CTSD</sub> | $C_{T}$ voltage shutdown threshold                                       | 1.8   | 2.1       | 2.4    | 2.2  | 2.3     | 2.4  |       |                                                     |

| V <sub>RT+</sub>  | High-level $R_T$ output voltage, $V_{CC}$ - $V_{RT}$                     |       | 10        | 50     |      | 10      | 50   |       | I <sub>RT</sub> = -100 μA                           |

| VRT+              |                                                                          |       | 100       | 300    |      | 100     | 300  |       | I <sub>RT</sub> = -1 mA                             |

| V <sub>RT-</sub>  | Low-level R <sub>T</sub> output voltage                                  |       | 10        | 50     |      | 10      | 50   |       | I <sub>RT</sub> = 100 μA                            |

| VRI-              | Low-level N1 output voltage                                              |       | 100       | 300    |      | 100     | 300  |       | I <sub>RT</sub> = 1 mA                              |

| V <sub>RTUV</sub> | UV-mode $R_T$ output voltage                                             |       | 0         | 100    |      | 0       | 100  | mV    | $V_{CC} \leq V_{CCUV}$                              |

|                   |                                                                          |       | 10        | 50     |      | 10      | 50   |       | I <sub>RT</sub> = -100 μA,<br>V <sub>CT</sub> = 0 V |

| V <sub>RTSD</sub> | SD-mode R <sub>T</sub> output voltage, V <sub>CC</sub> - V <sub>RT</sub> |       | 100       | 300    |      | 100     | 300  |       | I <sub>RT</sub> = -1 mA,<br>V <sub>CT</sub> = 0 V   |

**Comments:** The new IRS2153(1)D should fit into an existing design and maintain existing performance without any changes to the design with the exception of  $R_T/C_T$  value.

#### AN-1085

| Gate Drive      | r Output Characteristics                    |                 | IR215        | 3(1)/IR2    | 153(1)D      | IF           | RS2153(1)   | D            | Units | Test                                          |  |

|-----------------|---------------------------------------------|-----------------|--------------|-------------|--------------|--------------|-------------|--------------|-------|-----------------------------------------------|--|

| Symbol          | Definition                                  |                 | Min          | Тур         | Мах          | Min          | Тур         | Мах          | Units | Conditions                                    |  |

| $V_{OH}$        | High level output voltage                   |                 |              | 0           | 100          |              | VCC         |              |       | I <sub>0</sub> = 0 A                          |  |

| V <sub>OL</sub> | Low level output voltage, $V_{\rm O}$       |                 |              | 0           | 100          |              | СОМ         |              | mV    | I <sub>0</sub> = 0 A                          |  |

| $V_{OL_{UV}}$   | UV-mode output voltage, $V_{\rm o}$         |                 |              | 0           | 100          |              | СОМ         |              |       | $I_{O} = 0 \text{ A},$ $V_{CC} \leq V_{CCUV}$ |  |

| tr              | Output rise time                            |                 |              | 80          | 150          |              | 120         | 220          |       |                                               |  |

| t <sub>f</sub>  | Output fall time                            |                 |              | 45          | 100          |              | 50          | 80           | ns    |                                               |  |

| t <sub>sd</sub> | Shutdown propagation delay                  |                 |              | 660         |              |              | 350         |              |       |                                               |  |

| t <sub>d</sub>  | Output deadtime $(H_{o} \text{ or } L_{o})$ | 2153D<br>21531D | 0.75<br>0.35 | 1.20<br>0.6 | 1.65<br>0.85 | 0.65<br>0.35 | 1.10<br>0.6 | 1.75<br>0.85 | μs    |                                               |  |

| I <sub>O+</sub> | Output source current                       | •               |              |             |              |              | 180         |              | m 4   |                                               |  |

| I <sub>O+</sub> | Output sink current                         |                 |              |             |              |              | 260         |              | mA    |                                               |  |

**Comments:** Output rise and fall times are slightly longer due to a slight decrease in the output source and sink currents Deadtime tolerances had to be slightly downgraded, but should not impact most applications.

#### 3. Conclusions

In most cases, any member for the IR2153(1)/IR2153(1)D family will be easily and advantageously replaced by the new leadfree IRS2153(1)D. The application will benefit a monolithic solution integrating a bootstrap FET, an increased UVLO hysteresis, a possibility of non-latch IC shutdown, better thermal behavior and ROHS compatibility while keeping a 3% tolerance on the frequency.

International **TCR** Rectifier **IR WORLD HEADQUARTERS:** 233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105 *Data and specifications subject to change without notice.* 7/242006

#### AN-1085